1.1 实验目的

1) 熟悉多思计算机组成原理网络虚拟实验系统的使用方法。

2) 掌握全加器的逻辑结构和电路实现方法。

1.2 实验要求

1) 做好实验预习,复习全加器的原理,掌握实验元器件的功能特性。

2) 按照实验内容与步骤的要求,独立思考,认真仔细地完成实验。

3) 写出实验报告。

1.3 实验电路

本实验使用的主要元器件有:与非门、异或门、开关、指示灯。

一位全加器的逻辑结构如图 1.1 所示,图中涉及的控制信号和数据信号如下:

1) Ai、Bi:两个二进制数字输入。

2) Ci:进位输入。

3) Si:和输出。

4) Ci+1:进位输出。

1.4 实验原理

1 位二进制加法器有三个输入量:两个二进制数字 Ai、Bi 和一个低位的进位信号 Ci,这三个值相加产生一个和输出 Si 以及一个向高位的进位输出 Ci+1,这种加法单元称为全加器,其逻辑方程如下:

Si=Ai⊕Bi⊕Ci (1.1)

Ci+1=AiBi+BiCi+CiAi

1.5 实验内容与步骤

-

运行虚拟实验系统,从左边的实验设备列表选取所需组件拖到工作区中,按照图 1.1 所示搭建实验电路,得到如图 1.2 所示的实验电路。

-

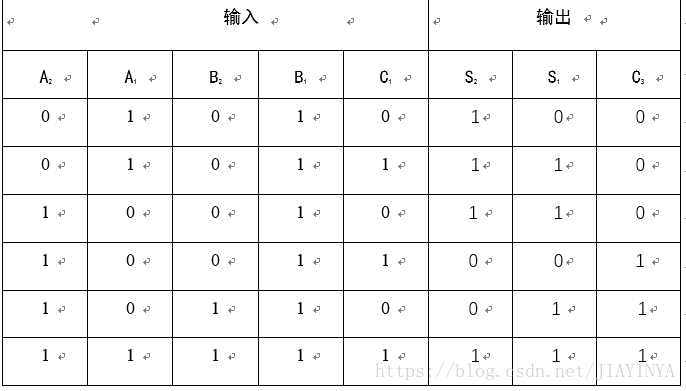

打开电源开关,按表 1-1 中的输入信号设置数据开关,根据显示在指示灯上的运算结果填写表 1-1 中的输出值。

-

关闭电源开关,增加元器件,实现一个 2 位串行进位并行加法器。用此加法器进行运算,根据运算结果填写好表 1-2。

*解题思路分析:

对于三个一位二进制a,b,c全加器,其中逻辑为异或。即是1异或0为1,0异或1为1。由图不难分析,先与非门逻辑再异或门逻辑,或是先异或门逻辑再与非门逻辑。也就不难得到如图所示的真值表。

对于一个2为串行进位并行加法器,将两个1位2进制加法器并联在一起。其中低位加法器的高位进位输出作为高位的输入C2.再分析异或门与非门的相关逻辑不难得出如图所示的2位串行进位并行加法器的真值表。*

1.6 思考与分析

- 串行进位并行加法器的主要缺点是什么?有改进的方法吗?

答:高位的运算必须等到低位的进位产生才能进行,因此运算速度较慢。改进方法:为了提高运算速度,可采用超前进位的方式,即每一位的进位根据各位的输入同时预先形成,而与低位的进位无关。 - 能使用全加器构造出补码加法/减法器吗?

答:可以。因为当前计算机中加法和减法都是通过加法器来实现的。数值一律用补码来存储可以将符号位和其他位一起处理,便于加法和减法运算。

总结及心得体会

这个实验主要考察了我们的电路设计和调试能力,通过一个简单加法器的形式,目的是为了让我们掌握电路设计和分析的方法和能力。为了对电路设计过程中遇到的问题作出一个较好地解决和解释,必须要对系统或者设计有着很清楚的认识。

通过这个实验,我查阅了书籍和网络资源,较清楚地了解了2位二进制加法器的功能和内部运算过程,这对我的研究能力和探知能力有着举足轻重的作用。实验电路设计之后,我对电路设计的流程以及过程中时常会遇到的问题进行了系统地归纳,这对我的以后的电路设计能力有着推动作用,也让我对电路设计的技巧有了较好地掌握

京公网安备 11010502036488号

京公网安备 11010502036488号