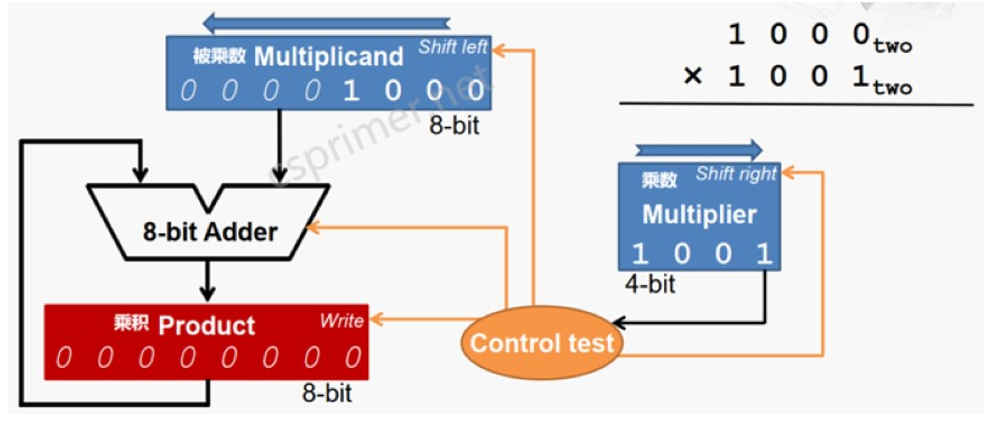

串行乘法器

因为早期晶体管数量大会产生大量的发热, 因此早期使用循环加法移位的方式实现乘法

乘数右移等价于取出每一位1, 被乘数左移, 相当于十进制做乘法过程中每选择一位要进行×10\times 10×10

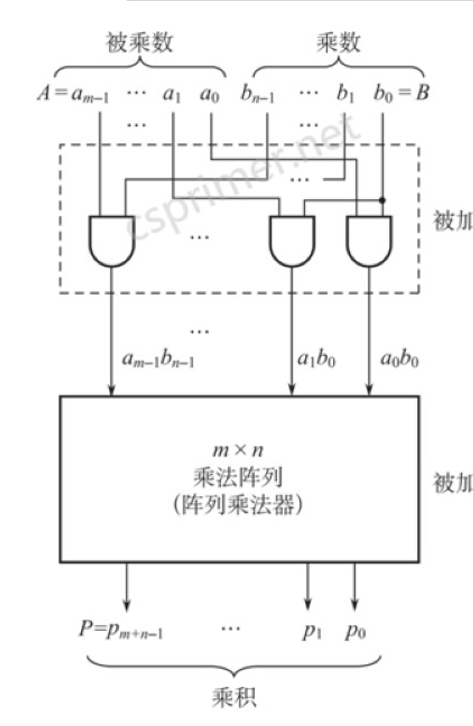

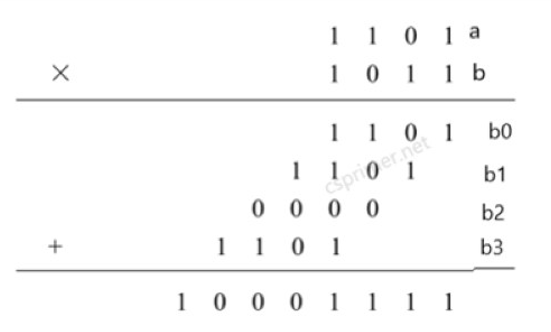

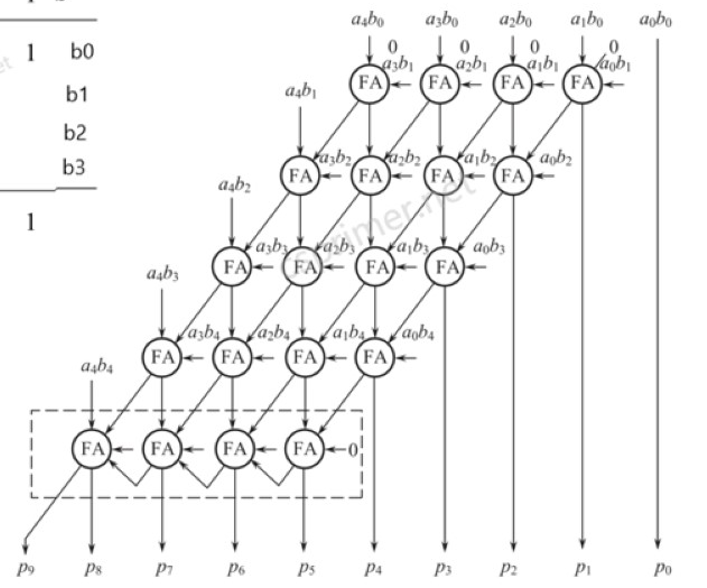

阵列并行乘法器

但是上述的计算过程是串行的, 需要O(n)O(n)O(n)的时间复杂度, 现在一般使用并行的方式计算

每一步的中间结果都可以通过and运算得到, 从乘数的位数从低到高, 相应的每次计算的结果都需要向左移动相应的位数

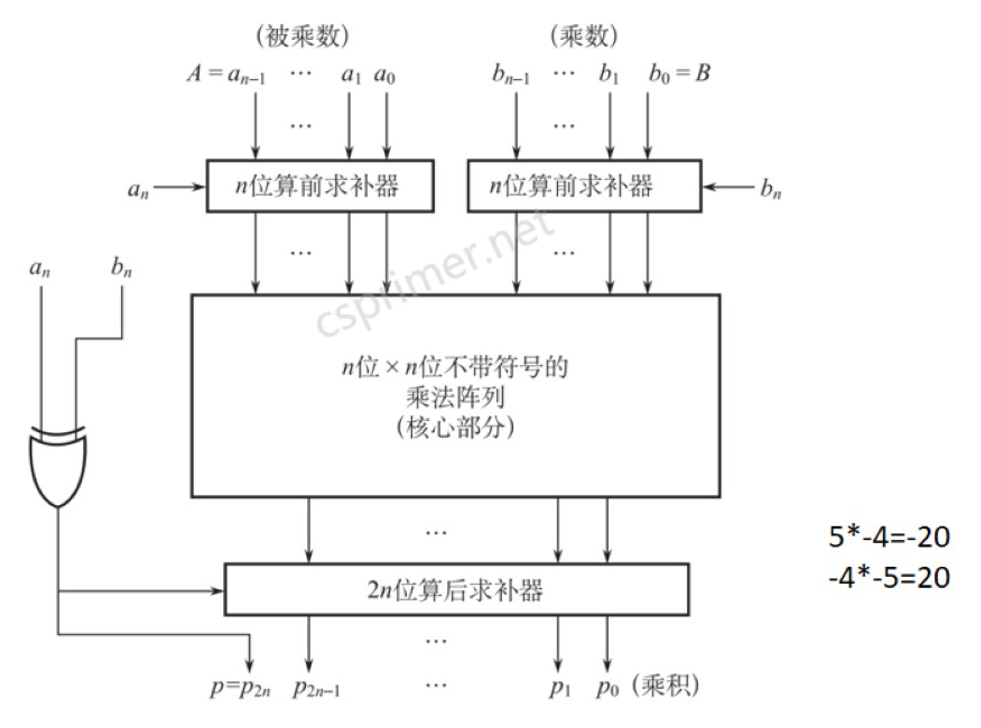

阵列乘法器的原理图如下

有符号的乘法

假设计算−4×5-4 \times 5−4×5, 首先将两个数字进行求补码, 也就是负数取反加一, 正数保持不变, 经过乘法器计算, 然后在最后检查两个输入的数字, 如果符号相同不做考虑, 如果符号不同对输出的结果取反加一, 使用异或门实现

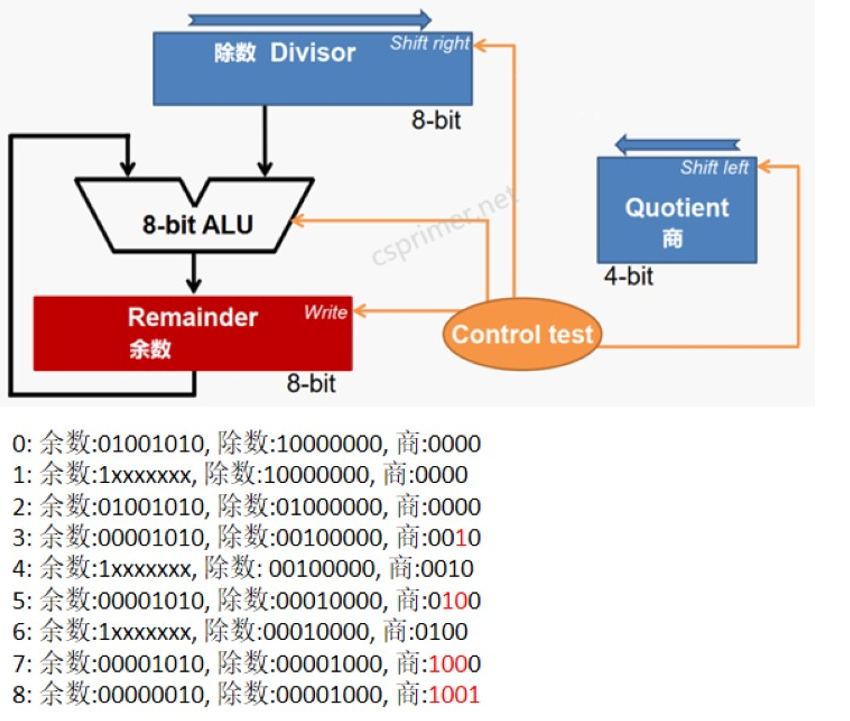

串行除法器

二进制除法的商是0或者1, 从最高位开始使得被除数和除数相减, 如果不够减将除数右移, 并且商是0, 直到够减或者除数和被除数最后一位对齐

控制信号可以控制除数和商做右移或者左移也可以控制ALU做加法或者减法, 也可以控制ALU的结果是否写入到余数寄存器当中

- 使用余数减去除数, 如果是负数, 说明不够减

- 控制ALU做加法, 将余数恢复, 接下来将除数右移一位, 将商左移一位

- 将余数减去除数, 因为除数进行了右移, 这时候是够减的, 得到余数

- 将商置

1并且将除数右移一位, 将商左移一位 - 重复上述流程

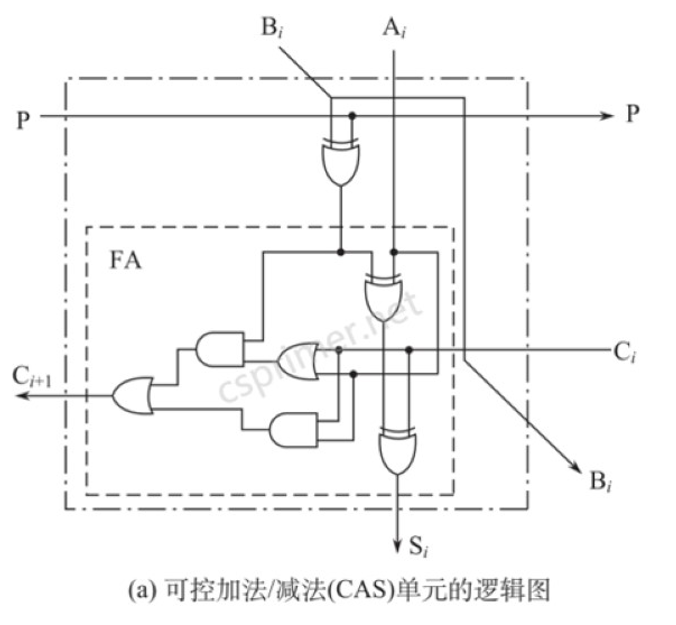

并行除法器

阵列除法器的核心部件CAS, 可以做加法或者减法, P端机型判断

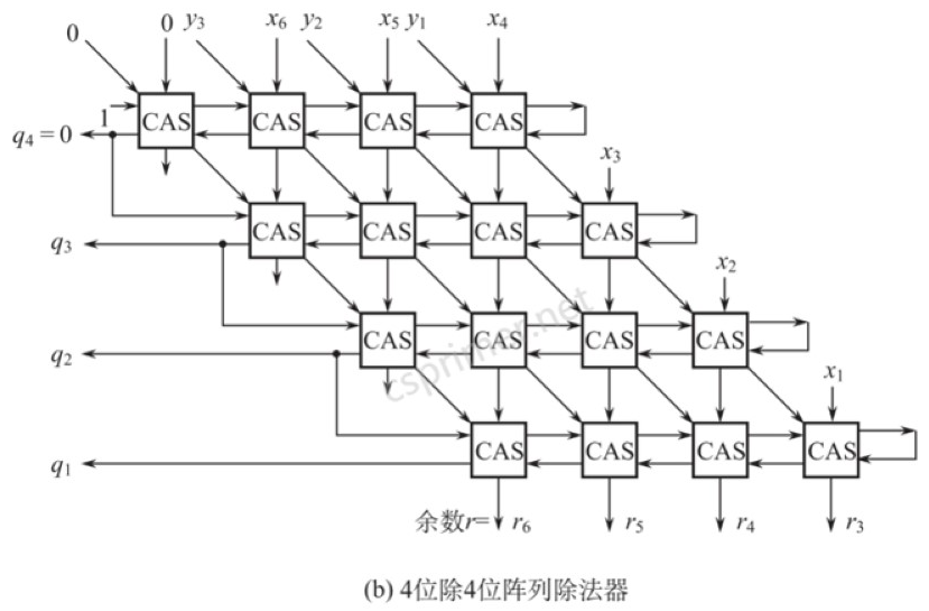

阵列除法器的原理图如下, 向右倾斜相当于除数向右移动

先做减法, 然后看余数是否是负数决定下一步做加法还是减法

先做减法, 然后看余数是否是负数决定下一步做加法还是减法

京公网安备 11010502036488号

京公网安备 11010502036488号