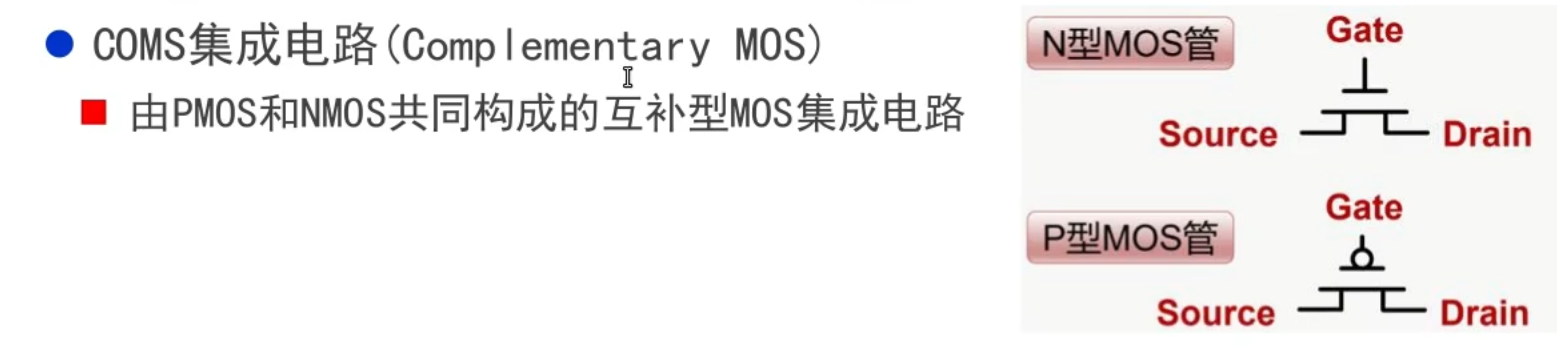

晶体管分类

晶体管分为NMOS和PMOS, Gate端是栅极控制是否导通, 还有源极和漏极

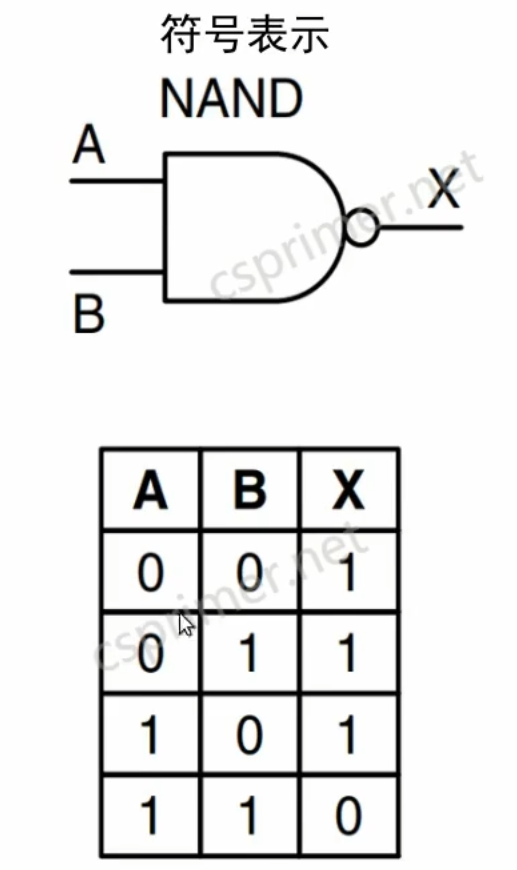

与非门的实现

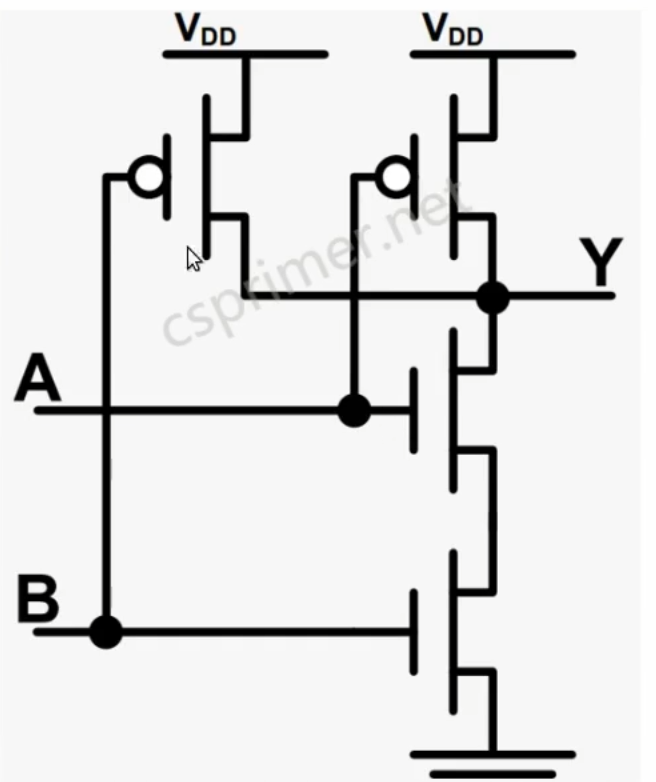

晶体管实现

上述PMOS管输入是1, NMOS输入是地面, 输入是0

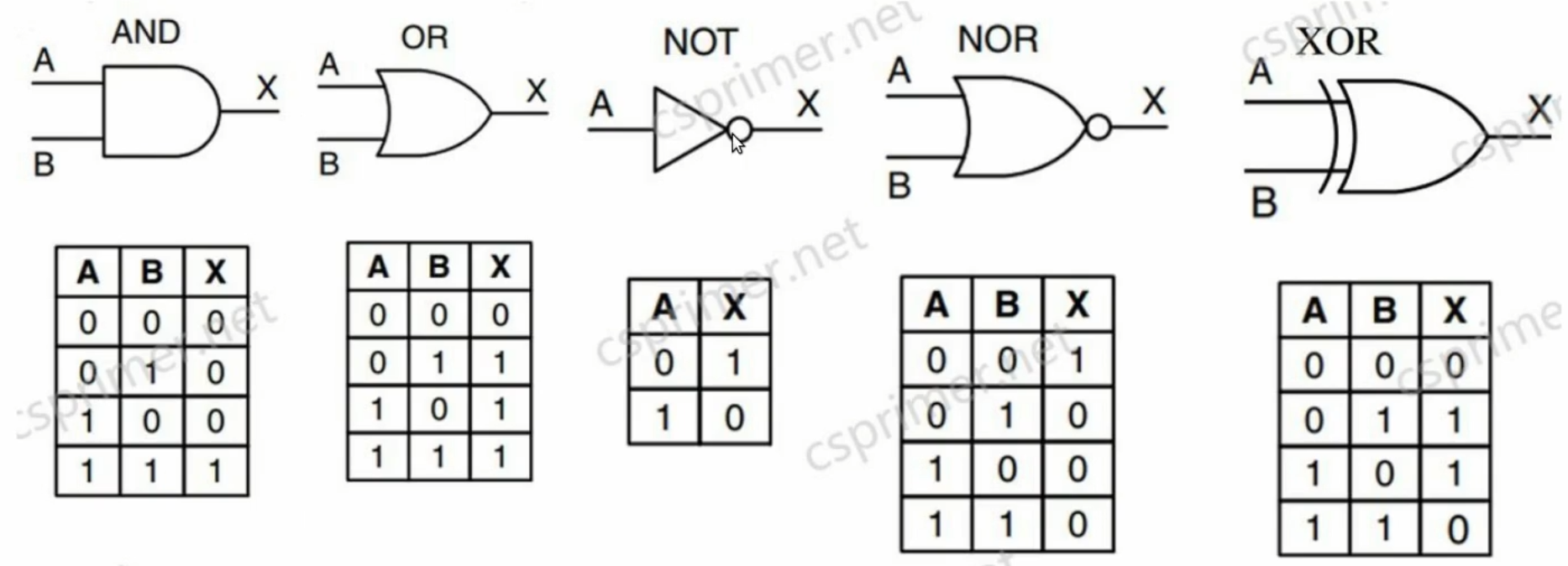

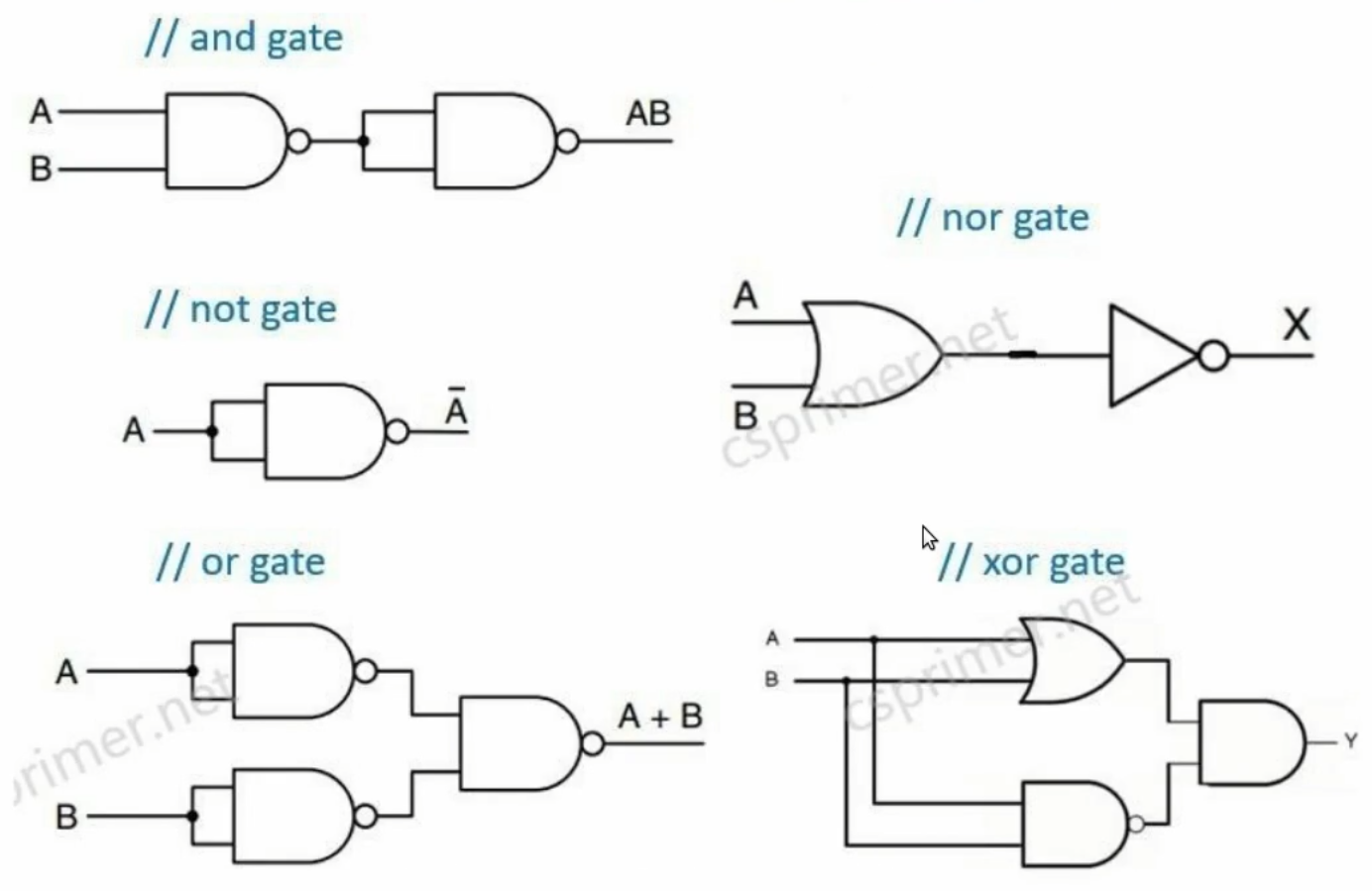

其余基本门电路

如下基本的门电路都可以由与非门组成

使用与非门构建其他基础逻辑门

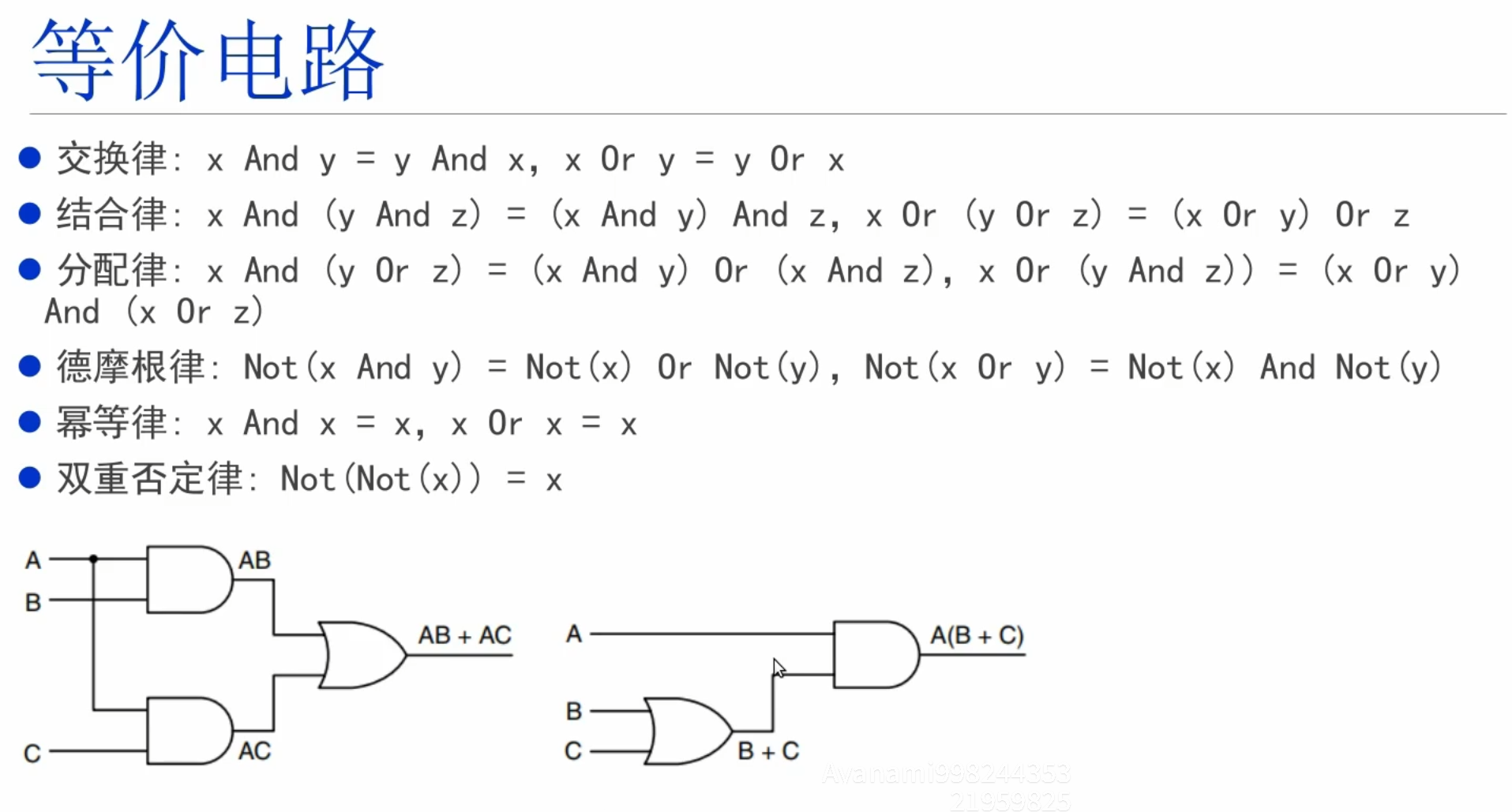

电路优化

实际设计过程中一般使用布尔运算优化电路, 减少晶体管数量

硬件描述语言HDL

HDL的语句顺序不重要, 只描述门电路之间的连接, 使用iverilog进行仿真验证

电路验证

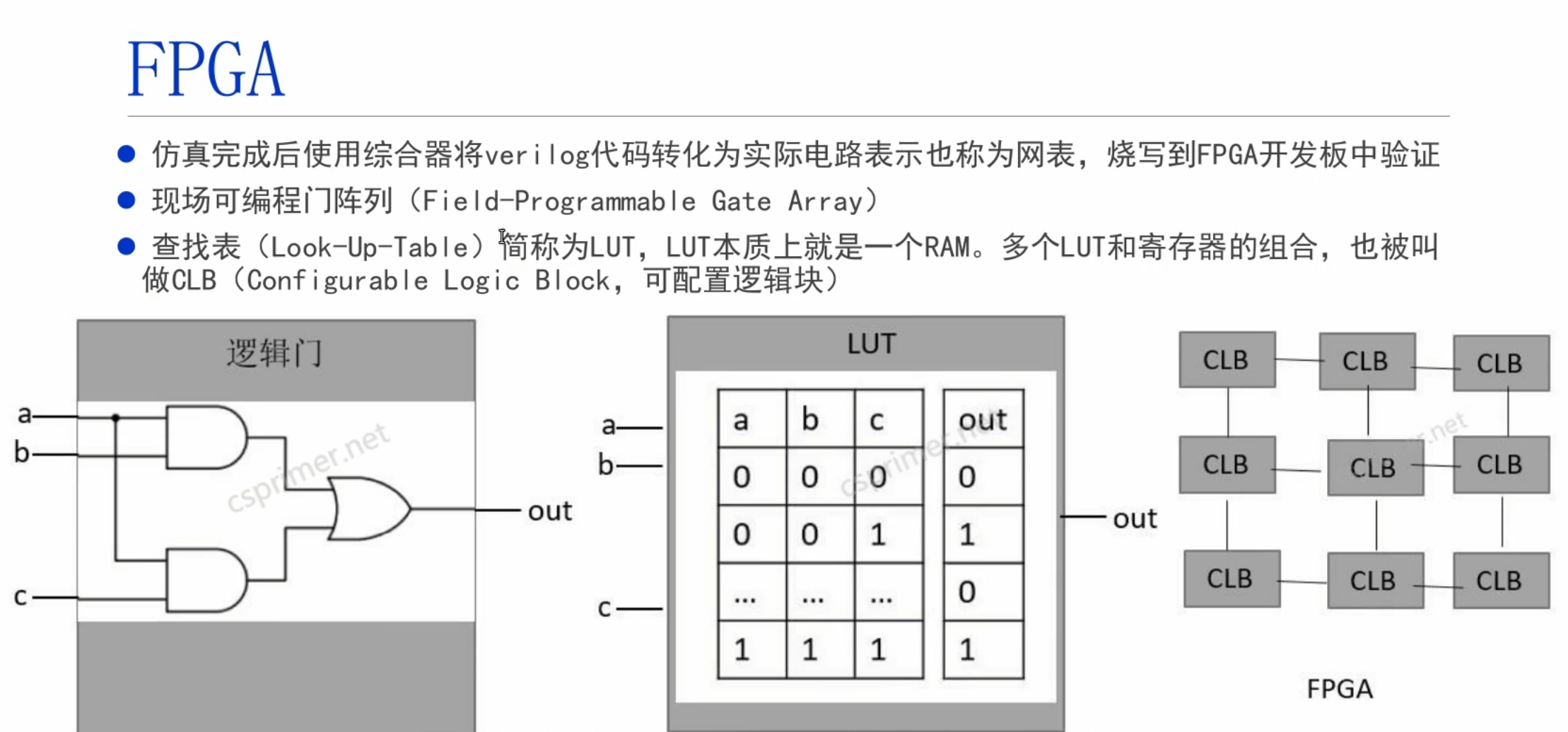

FPGA是一个查找表的结构本质是一个RAM, 可以不更改硬件焊接连接的情况测试硬件电路

使用Verilog编写逻辑门代码实现基础逻辑门

使用MOS管构建与非门

代码实现, wire代表的是连线, 类似于C语言的中间变量, 两个NMOS管串联, 两个PMOS管并联

`ifndef A_NAND_V

`define A_NAND_V

module a_nand(output o, input a, input b);

wire w;

supply1 vdd;

supply0 gnd;

pmos (o, vdd, a);

pmos (o, vdd, b);

nmos (w, gnd, a);

nmos (o, w, b);

endmodule

`endif

测试

`include "a_nand.v"

module nand_tb;

reg a, b;

wire out;

a_nand obj(out, a, b);

initial begin

// 将 $monitor 放在最开始,确保能监控到所有变化

$monitor("Time=%0t: a=%b, b=%b, out=%b", $time, a, b, out);

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

endmodule

使用与非门构建与门

代码实现

`ifndef A_AND_V

`define A_AND_V

`include "a_nand.v"

module a_and(output o, input a, b);

wire w;

a_nand a1(w, a, b);

a_nand a2(o, w, w);

endmodule;

`endif // A_AND_V

测试

`include "a_and.v"

module and_tb;

reg a, b;

wire out;

a_and obj(out, a, b);

initial begin

// 将 $monitor 放在最开始,确保能监控到所有变化

$monitor("Time=%0t: a=%b, b=%b, out=%b", $time, a, b, out);

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

endmodule

与非门构建或门

代码实现

`ifndef A_OR_V

`define A_OR_V

`include "a_nand.v"

module a_or(output o, input a, b);

wire w1, w2, w3;

a_nand n1(w1, a, a);

a_nand n2(w2, b, b);

a_nand n3(o, w1, w2);

endmodule;

`endif

测试

`include "a_or.v"

module or_tb;

reg a, b;

wire out;

a_or obj(out, a, b);

initial begin

// 将 $monitor 放在最开始,确保能监控到所有变化

$monitor("Time=%0t: a=%b, b=%b, out=%b", $time, a, b, out);

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

endmodule

与非门构建非门

代码实现

`ifndef A_NOT_V

`define A_NOT_V

`include "a_nand.v"

module a_not(output o, input a);

a_nand n1(o, a, a);

endmodule;

`endif // A_NOT_V

测试

`include "a_not.v"

module not_tb;

reg a;

wire out;

a_not obj(out, a);

initial begin

// 将 $monitor 放在最开始,确保能监控到所有变化

$monitor("Time=%0t: a=%b, out=%b", $time, a, out);

a = 0; #10;

a = 0; #10;

a = 1; #10;

a = 1; #10;

$finish;

end

endmodule

构建或非门

代码实现

`include "a_or.v"

`include "a_not.v"

module a_nor(output o, input a, b);

wire w;

a_or o1(w, a, b);

a_not n1(o, w);

endmodule

测试

`include "a_nor.v"

module or_tb;

reg a, b;

wire out;

a_nor obj(out, a, b);

initial begin

// 将 $monitor 放在最开始,确保能监控到所有变化

$monitor("Time=%0t: a=%b, b=%b, out=%b", $time, a, b, out);

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

endmodule

构建异或门

代码实现

`ifndef A_XOR_V

`define A_XOR_V

`include "a_and.v"

`include "a_or.v"

`include "a_not.v"

module a_xor(output o, input a, b);

wire a1, b1;

a_not n1(a1, a);

a_not n2(b1, b);

wire val1, val2;

a_and and1(val1, a1, b);

a_and and2(val2, a, b1);

a_or or1(o, val1, val2);

endmodule

`endif

测试

`include "a_xor.v"

module xor_tb;

reg a, b;

wire out;

a_xor obj(out, a, b);

initial begin

// 将 $monitor 放在最开始,确保能监控到所有变化

$monitor("Time=%0t: a=%b, b=%b, out=%b", $time, a, b, out);

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

endmodule

京公网安备 11010502036488号

京公网安备 11010502036488号