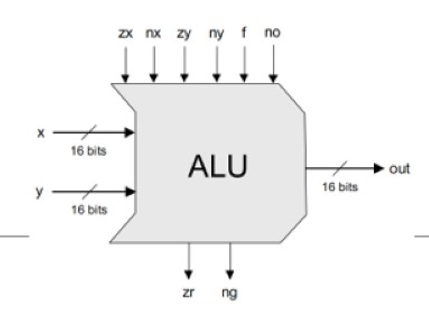

算术逻辑单元ALU

C指令的6位对应ALU的6个控制输入

控制输入的前面4位是对输入的数据进行预处理, no标志是结果是否取反

- zx 为1, 将x的值设置为0

- nx为1, 将x的值设置为

~x - zy为1, 将y的值设置为0

- ny为1, 将y的值设置为

~y

如果f为1, 执行x + y, 否则执行x & y, 这里的x和y是前面处理后的

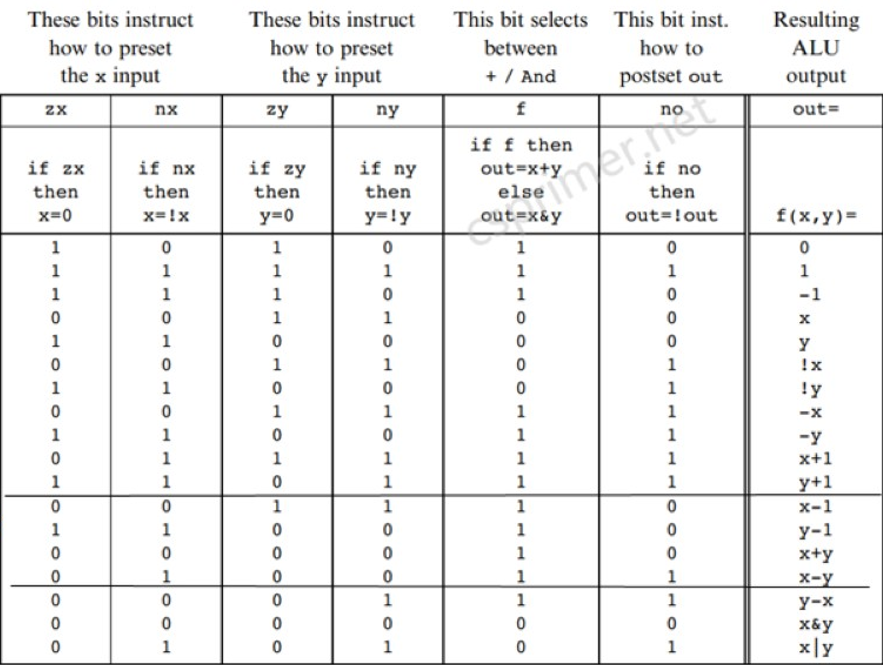

得到如下的表

观察y + 1, x置0并且取反并且与!y相加, 结果再取反, 实际的表达式是~(~0 + ~y)也就是y + 1

观察x - y, 首先将x取反, 并且是相加状态, 然后将结果取反, 实际就是~(~x + y), 也就是x - y

为什么要这样设计ALU? 因为这样设计后ALU只需要实现置0, 取反, 相加, 与操作就能组合出复杂的操作, 简化硬件电路的实现

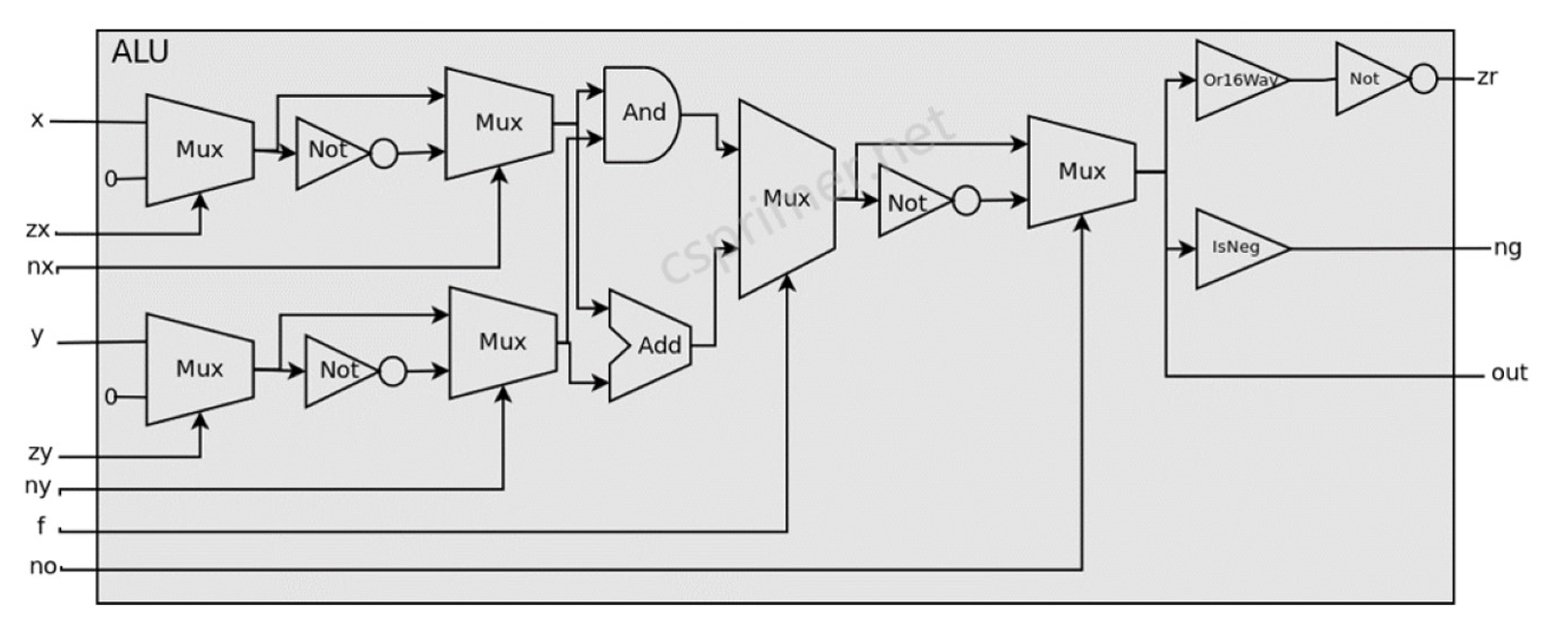

ALU的控制

使用多路选择器实现上述的各种判断

zr输出结果是否是0, ng判断结果是否是负数

代码实现

`ifnde***_V

`define ALU_V

`include "add16.v"

`include "mux16.v"

`include "not16.v"

`include "and16.v"

`include "a_or.v"

`include "or16.v"

`include "a_not.v"

module alu(output [15:0] out,

output zr, ng,

input [15:0] x, y,

input f, zx, nx, zy, ny, no);

wire [15:0] newx, newy;

mux16 mux0(newx, x, 16'b0, zx);

mux16 mux1(newy, y, 16'b0, zy);

wire [15:0] newx_not, newy_not;

not16 not0(newx_not, newx);

not16 not1(newy_not, newy);

wire [15:0] val1, val2;

mux16 mux2(val1, newx, newx_not, nx);

mux16 mux3(val2, newy, newy_not, ny);

wire [15:0] res1, res2;

wire c;

wire [15:0] res, res_not;

and16 and0(res1, val1, val2);

add16 add0(res2, c, val1, val2, 1'b0);

mux16 mux4(res, res1, res2, f);

not16 not2(res_not, res);

mux16 mux5(out, res, res_not, no);

assign ng = out[15] == 1 ? 1 : 0;

wire zr_not;

or16 or0(zr_not, out);

a_not not3(zr, zr_not);

endmodule;

`endif

测试

京公网安备 11010502036488号

京公网安备 11010502036488号